Binome2020-4 : Différence entre versions

(iai) |

|||

| Ligne 87 : | Ligne 87 : | ||

===Breakout de la mémoire=== | ===Breakout de la mémoire=== | ||

| − | + | Un PCB breakout de la Nand MT29F8G compatible pour Breadboards a été conçu : il est disponible ici [[File:nand_breakout.zip]]. Dans notre cas, il a été fabriqué au sein des locaux de Polytech. [[File:breakout.png|right|250px]]<br>[[File:fab_breakout.png|right|250px]] | |

| + | Assemblé avec un module [https://www.amazon.fr/Espressif-ESP32-S2-Saola-1M-Carte-de-d%C3%A9veloppement/dp/B087T2NTD6/ref=sr_1_3?dchild=1&keywords=esp32-s2&qid=1618154099&sr=8-3 ESP32-S2 Saola 1M] sur une breadboard, on obtient le montage suivant : <br> | ||

| + | [[File:debug_board.png|left|250px]] | ||

| + | |||

| + | ===Analyse des signaux=== | ||

| + | Le code rédigé était d'abord testé sur la clé. Cependant, suite à des blocages, une analyse des signaux était nécessaire. En effet, nous n'arrivions pas à envoyer des commandes à la clé (Latch d'écriture lorsque signal montant selon la datasheet, mais descendant selon la réalité). | ||

| + | {| |- style="font-size: 87%; text-align: center; margin-left:0.2em; border: 1px solid #bbb;" | ||

| + | | valign="center" | Cannel 0 | ||

| + | | valign="center" | Write Protect (Inversé) | ||

| + | |- | ||

| + | | valign="center" | Cannel 1 | ||

| + | | valign="center" | Write Enable (Inversé) | ||

| + | |- | ||

| + | | valign="center" | Cannel 2 | ||

| + | | valign="center" | Address Latch Enable | ||

| + | |- | ||

| + | | valign="center" | Cannel 3 | ||

| + | | valign="center" | Command Latch Enable | ||

| + | |- | ||

| + | | valign="center" | Cannel 4 | ||

| + | | valign="center" | Chip Enable (Inversé) | ||

| + | |- | ||

| + | | valign="center" | Cannel 5 | ||

| + | | valign="center" | Read Enable (Inversé) | ||

| + | |- | ||

| + | | valign="center" | Cannel 6 | ||

| + | | valign="center" | VCC | ||

| + | |- | ||

| + | | valign="center" | Cannel 7 | ||

| + | | valign="center" | Ready/[Busy (Inversé)] | ||

| + | |- | ||

| + | | valign="center" | Cannel 8-15 | ||

| + | | valign="center" | IO0-7 | ||

| + | |}<br> | ||

| + | |||

| + | [[File:debug_signal.png|left|250px]] | ||

Version du 11 avril 2021 à 17:59

Sommaire

Introduction

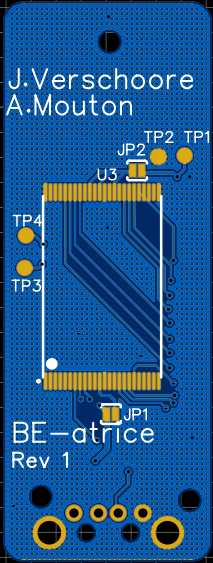

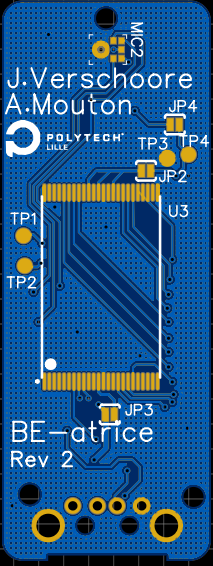

Au cours de ce BE, nous (Albin Mouton et Jérémy Verschoore de la Houssaye) avons décidé de concevoir une clé USB disposant d'une mémoire de 8Go, pouvant se connecter à un réseau WiFi, afin de permettre un accès à distance de son contenu.

De plus nous espérons pouvoir ajouter une fonctionnalité microphone, permettant d'enregistrer l'utilisateur (à son insu ?)

Composants utilisés

Composants clés

- Microcontrôleur : ESP32-S2 (package WROVER 4MB)

- dispose d'une interface Wi-Fi Station + Point d'accès

- dispose de ports I2S (entrée et sortie)

- dispose d'une interface USB.

- Mémoire : MT29F8G

Autres

- Régulateur : LDO (3.3V)

- Boutons pour la programmation

- Microphone : SPH0645LM4H (communiquant en I2S)

Révisions

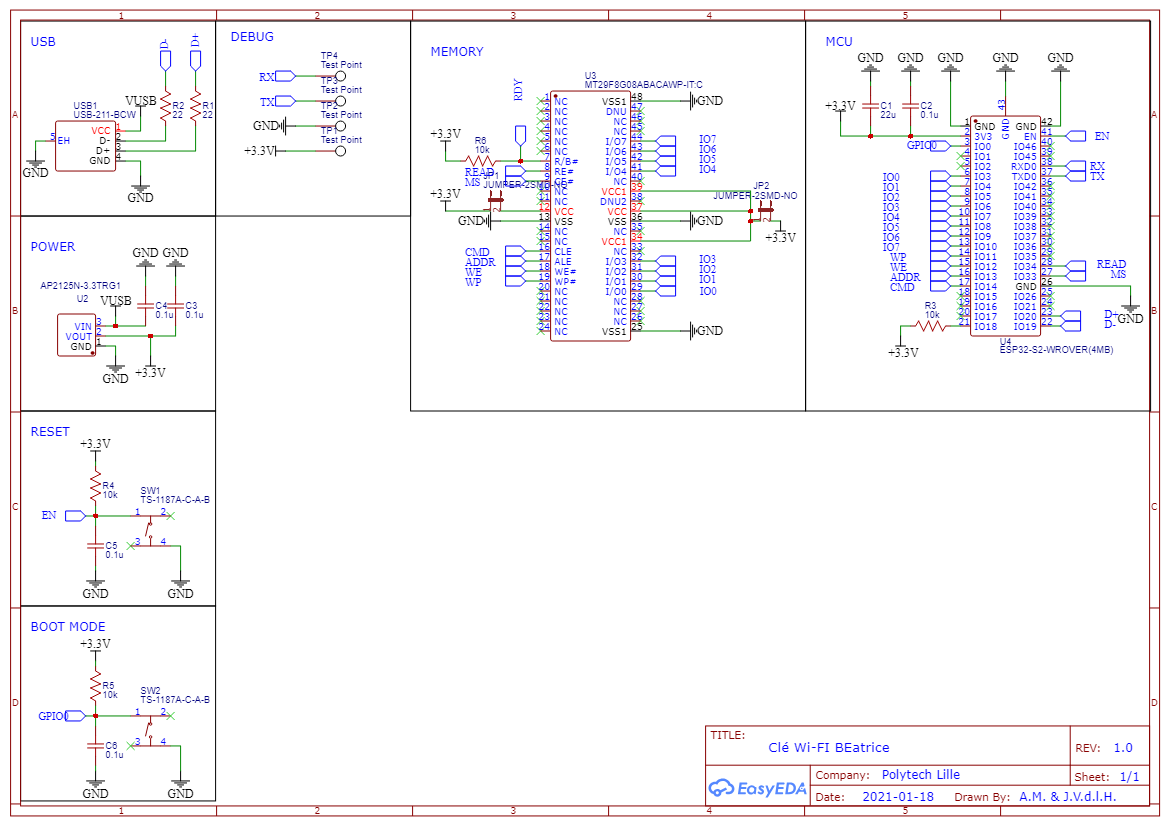

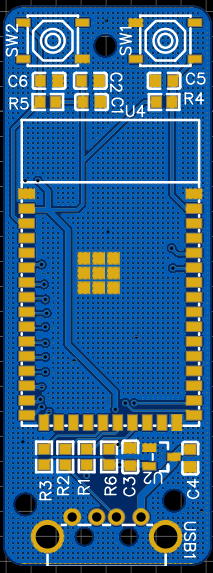

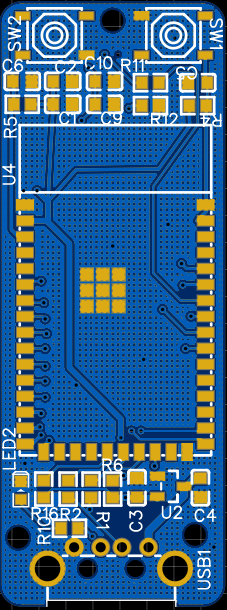

Rev 1

Version la plus simple de la clé, ne pouvant que servir de disque avec accès à distance.

|

|

Gerber : Fichier:Rev1 PCB.zip

Abandonnée pour la Rev 2 le 25/01

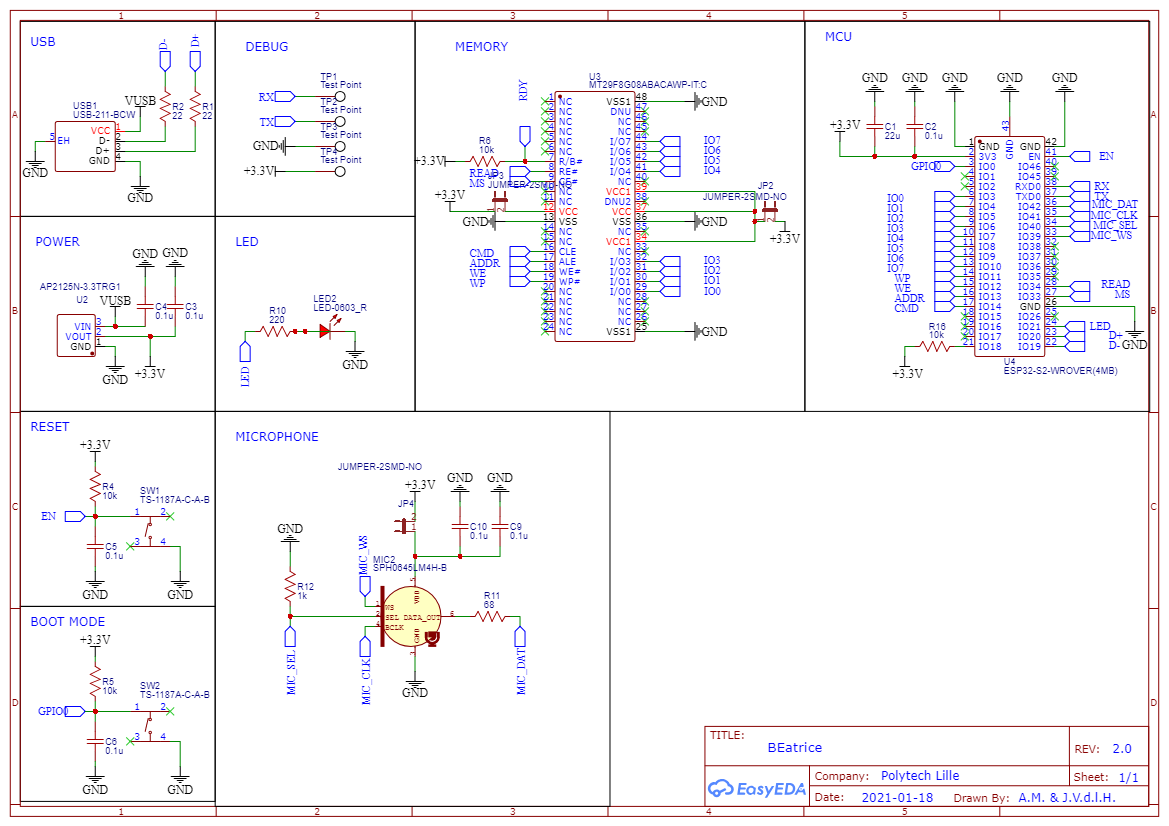

Rev 2

Ajout d'un microphone et d'une LED de statut. (Ainsi qu'un magnifique logo)

|

|

Gerber

Version actuelle

Programmation

Explications

Environnement de développement

Pour programmer l'ESP32S2 nous utiliserons l'ESP-IDF. Celui-ci est disponible pour Linux, Mac et Windows.

Téléversement vers la carte

Afin de téléverser le programme vers la carte, il faut tout d'abord la passer en mode programmation lorsque celle-ci boot. Pour ce faire le GPIO 0 doit être relié au 0V lors du démarrage. Le bouton SW2 de notre carte est prévu à cet effet.

Il faut donc maintenir enfoncé SW2 pour passer le GPIO 0 à 0V, puis appuyer succinctement sur le SW1 (qui est le reset de la carte) pour la redémarrer. Une fois fait on peut relâcher SW2. La carte est en mode programmation.

Il existe deux moyens pour téléverser son programme une fois compilé :

- Via une interface série FTDI, à connecter aux Test Points comme ceci :

| Clé USB | TP3 | TP4 | TP2 | TP1 |

| FTDI | GND | 3V3t fait) | RX | TX |

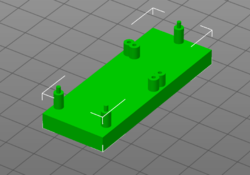

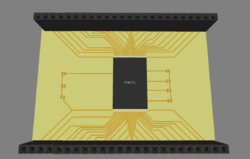

Nous avons conçu une plateforme de programmation imprimée en 3D pour simplifier la procédure :

- Directement via le port USB en le programmant par DFU (plus simple)

Debug mémoire

Lors de la programmation de la clé USB, nous avons rencontré des problèmes de communication avec la mémoire. Pour pouvoir analyser les signaux, nous avons développé une version breakout de notre clé USB, afin d'y connecter un analyseur logique (Hantek6022BL)

Breakout de la mémoire

Un PCB breakout de la Nand MT29F8G compatible pour Breadboards a été conçu : il est disponible ici Fichier:Nand breakout.zip. Dans notre cas, il a été fabriqué au sein des locaux de Polytech.Assemblé avec un module ESP32-S2 Saola 1M sur une breadboard, on obtient le montage suivant :

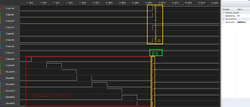

Analyse des signaux

Le code rédigé était d'abord testé sur la clé. Cependant, suite à des blocages, une analyse des signaux était nécessaire. En effet, nous n'arrivions pas à envoyer des commandes à la clé (Latch d'écriture lorsque signal montant selon la datasheet, mais descendant selon la réalité).

| Cannel 0 | Write Protect (Inversé) |

| Cannel 1 | Write Enable (Inversé) |

| Cannel 2 | Address Latch Enable |

| Cannel 3 | Command Latch Enable |

| Cannel 4 | Chip Enable (Inversé) |

| Cannel 5 | Read Enable (Inversé) |

| Cannel 6 | VCC |

| Cannel 7 | Ready/[Busy (Inversé)] |

| Cannel 8-15 | IO0-7 |