Binome2019-3 : Différence entre versions

| Ligne 57 : | Ligne 57 : | ||

Esquisse du schéma de notre nouveau circuit: | Esquisse du schéma de notre nouveau circuit: | ||

| − | [[Fichier: | + | [[Fichier:esquisse1.jpg]] |

Version du 16 février 2020 à 13:51

Sommaire

Définition du projet

Nous avons deux possibilités de taille de mémoires: une de 16Mo et une de 16Go, et nous allons réaliser notre clé avec la mémoire 16Go (128Gb). Ce choix va nous demander une programmation plus complète car la puce n'est pas pré-programmée pour la mémoire en question, mais nous pensons cette configuration d'une meilleure utilité.

Périphériques supplémentaires:

Afficheurs 7 segments permettant d'afficher la taille restante. Nous prévoyons entre deux et quatre afficheurs accolés permettant une meilleure précision. On aura donc besoin de 7 sorties pour l'afficheur (voire 8 si on utilise le point) plus 1 sortie par afficheur pour se placer sur celui voulu. Ainsi, si on choisi d'utiliser deux afficheurs accolés, on aura besoin de 7+2=9 sorties. Si on choisi d'en installer 4, on aura 7+4=11 sorties (+1 si point). Nous aurons donc probablement besoin de deux puces.

Périphériques optionnels:

Si le temps nous le permet, nous avons pour idée d'ajouter une petite batterie associée à un bouton permettant d'afficher la place restante même si la clé n'est pas branchée à un ordinateur.

Référencement des périphériques

Voici le choix favori pour les afficheurs: https://fr.farnell.com/multicomp/lt0565srwk/afficheur-sept-segments-rouge/dp/2627649

Cet afficheur contient 3 surfaces accolées et nécessiterait donc avec le point 8+3=11 sorties.

En ce qui concerne la mémoire, nous allons utiliser la mémoire MTF29F128G08, qui est la version 128Gb.

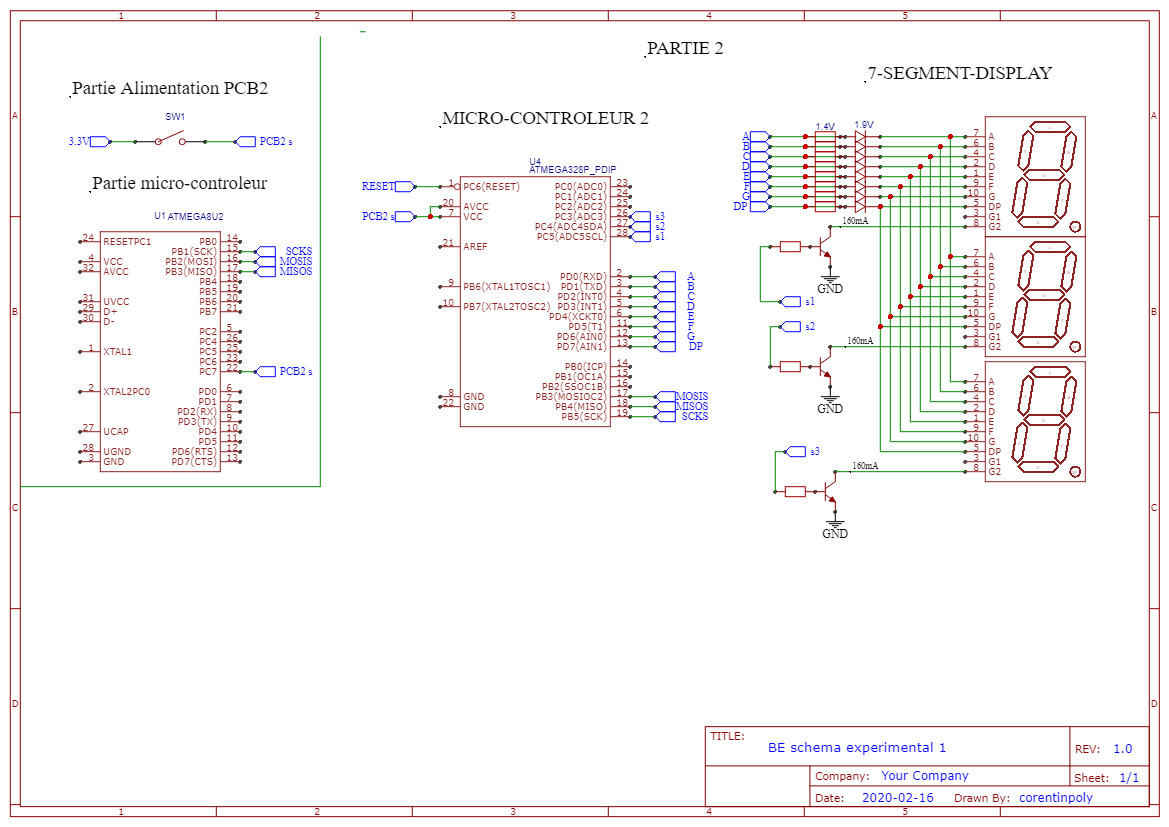

Nous allons utiliser une puce ATMEGA8U2 en tant que puce principale pour le contrôle des principales fonctions de la clé ainsi qu'en tant que puce mère pour la seconde, une ATMEGA328P, qui servira au contrôle de l'afficheur.

Conception électronique

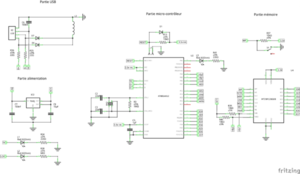

L'architecture électronique globale, qui ne concerne uniquement les fonctionnalités premières (micro-contrôleur maître et puce mémoire) peut être reprise ici:

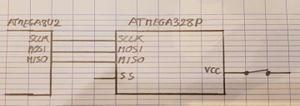

Les trois sorties disponibles en haut du micro-contrôleur seront utilisées pour une communication SPI avec le second.

Voici un premier jet de l'architecture de la communication entre les deux micro-contrôleurs:

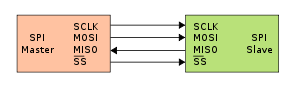

On note que l'entrée Vcc représente l'entrée d'un interrupteur qui actionnera l'afficheur. On voit également les trois sorties SPI utilisées, dont la MOSI (Master Output Slave Input) et MISO (Master Input Slave Output) servent respectivement à la communication de la puce mère vers la puce fille et de la puce fille vers la puce mère, comme le montre le schéma ci-dessous (la sortie et l'entrée SS ne seront pas utilisées):

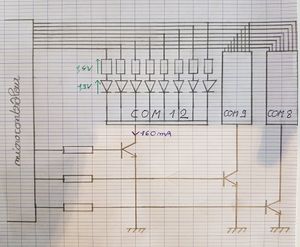

Ici, un premier jet de l'architecture de l'interface entre le deuxième micro-contrôleur et l'afficheur:

Les éléments COM12 ,COM9 et COM8 sont les trois cellules de notre afficheur. Les tensions entrantes (5V ou 3.3V) ne correspondant par à la tension préconisée pour l'afficheur (1.85=1.9V typ; 2,5V max), des résistances de 75 Ohm avec une tension de 1,4V à leurs bornes sont donc représentées.

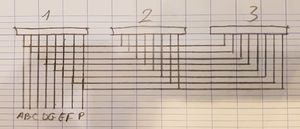

Enfin, voici un schéma de l'architecture de l'afficheur en question:

Ces schémas seront réalisés ultérieurement par ordinateur grâce à un logiciel spécifique.

Esquisse du schéma de notre nouveau circuit:

Programmation

Chronologie

27/01 Définition des principaux axes pour notre projet: choix de la carte mémoire, choix des périphériques spécifiques à notre clé et mise en place de notre Wiki.

10/02 Choix de l'afficheur 7-segments. Réflexions sur les liens entre les deux puces et entre la puce 328P et l'afficheur. Réalisation des premiers schémas de l'architecture électronique associée à ces parties et détermination de quelques caractéristiques (quelques valeurs des résistances nécessaires...)